概览

更新于 2015.05.03

F-I-L是一个开源的FPGA图像处理库,它提供了许多IP核,每一个IP核都拥有着它们自己的软件仿真、HDL功能仿真和板上测试。

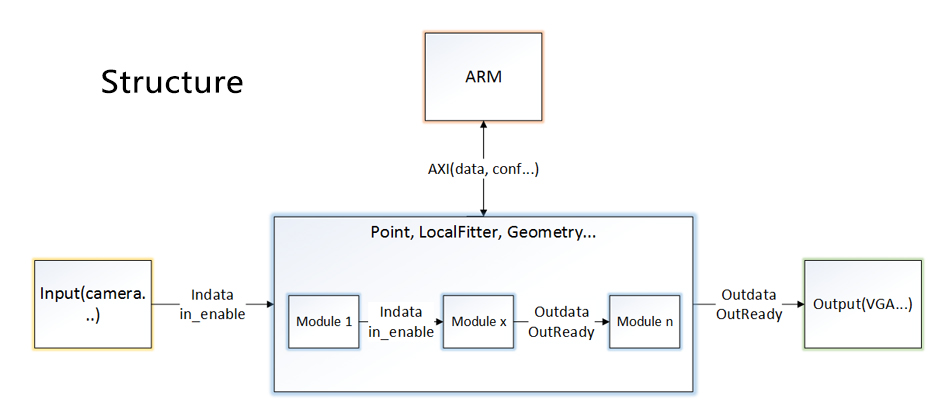

F-I-L的结构如下:

图像的数据源来自于摄像头或者其他硬件设备,随后这些数据将会被F-I-L中的IP核进行处理,最终输出到显示器或者其他设备。

同时,如何你使用软核或者硬核的Soc(片上系统),比如ZYNA平台、mircoblaze平台,你还可以通过AXI总线让这些IP与ARM等CPU去配置这些IP核,它有着巨大的灵活性。

支持

现在,仅仅有Xilinx公司的Vivado开发套装被支持,如果你想将这些IP使用在别的平台上,你可以将HDL文件剥离出来,并自行封装成其他IP,但是根据LGPL协议,你必须要公开你的源代码。

依赖

我使用Python2.7和PIL(Python Imaging Library)库进行软件仿真,同时使用modelsim SE 10.1进行HDL功能仿真,所以为了仿真,您必须准备好这两个环境。

不仅如此,功能仿真依赖于Xilinx的IP库,所以您必须将所有的Xilinx IP核编译到modelsim内,在Vivado里面,你只需要在它的控制台中输入以下指令就可以了:

compile_simlib -directory <library_output_directory> -simulator <agr>

-simulator_exec_path<sim_install_location>

之后,在modelsima安装目录中打开modelsim.ini文件(去掉只读属性),然后粘贴下列语句:

[Library]

std = $MODEL_TECH/../std

ieee = $MODEL_TECH/../ieee

verilog = $MODEL_TECH/../verilog

vital2000 = $MODEL_TECH/../vital2000

std_developerskit = $MODEL_TECH/../std_developerskit

synopsys = $MODEL_TECH/../synopsys

modelsim_lib = $MODEL_TECH/../modelsim_lib

simprim_ver = G:/EDA/Xilinx/simprim_ver(库的路径,以下同)

unisim_ver = G:/EDA/Xilinx/unisim_ver

xilinxcorelib_ver = G:/EDA/Xilinx/xilinxcorelib_ver

最后,还原只读属性即可。

教程

这里记录了一些在FPGA上实现图像处理的教程,现在仅仅支持中文:

许可

Copyright © 2015, 戴天宇 (dtysky). 拥有所有权利。

这个项目是自由软件并且遵从 GNU Lesser General Public License (LGPL)协议.